行业新闻 2025-06-10

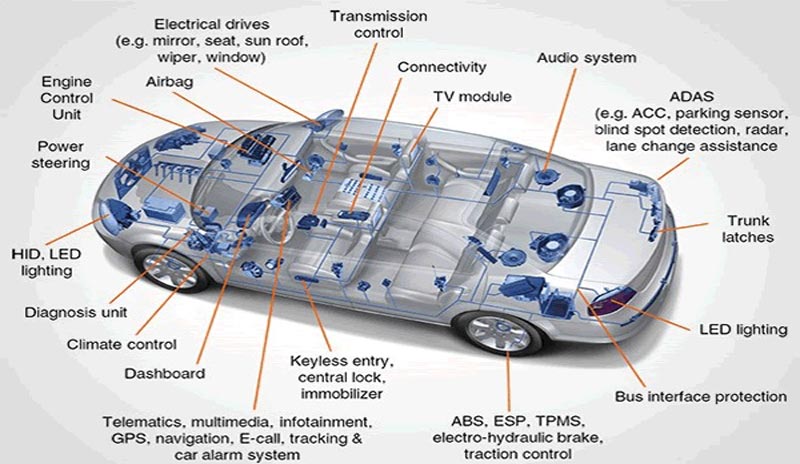

在当前的国际国内形势下,中国一直在加大对半导体芯片行业的支持力度,加强自主创新能力建设,突破关键核心技术瓶颈,实现半导体芯片行业的自主可控和可持续发展。这不仅关乎中国科技和经济的未来,也将为全球科技产业的发展作出重要贡献。

发展芯片产业的重要性在于从受制于人的困境中突围,保障国家信息安全,促进经济转型和产业发展,提升国际竞争力,抓住全球产业转移机遇,培养专业人才并推动创新驱动。当前,中国面临国外技术封锁的严峻形势,关键技术如高端芯片制造设备和先进封装技术被限制出口,导致国内企业如华为在芯片供应上遭遇断供危机。这凸显了自主研发芯片的紧迫性,因为芯片作为现代科技的核心,广泛应用于通信、金融、能源、军事等关键领域,一旦依赖进口,其潜在的安全漏洞和后门将严重威胁国家信息安全。

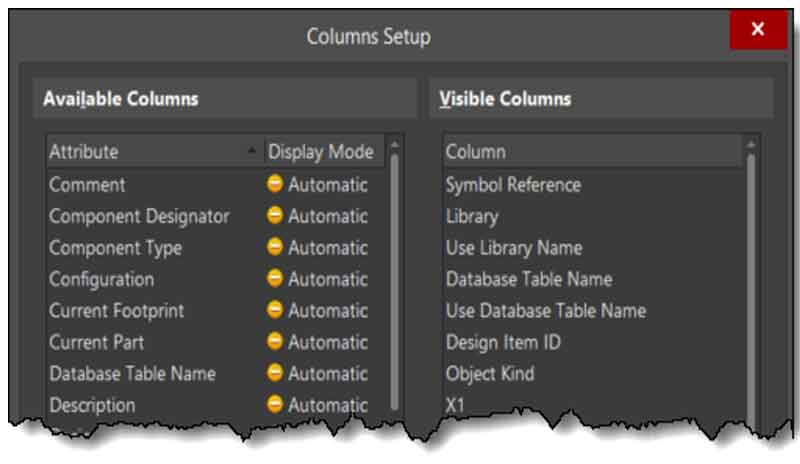

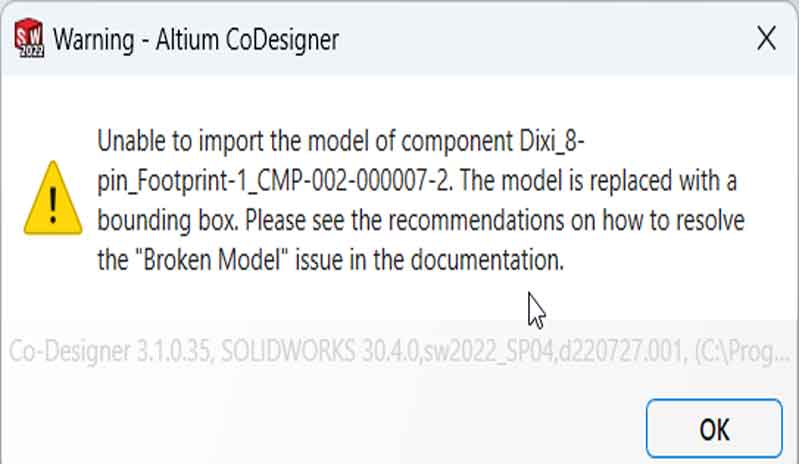

如今半导体芯片行业蓬勃发展的背景下,芯片封装测试作为关键环节,对产品的性能、可靠性和上市时间有着至关重要的影响。随着芯片技术的不断进步,从裸片制造到最终产品封装测试的整个流程都面临着日益复杂的挑战。Altium Designer 软件以其优越的功能和高度集成的设计环境,成为了半导体芯片封装测试行业的理想选择和得力助手,尤其在版本控制、装配变量、极坐标应用和 Wire Bonding 等方面,为芯片封装测试提供了精准且高效的解决方案。助力企业提升封测效率、降低迭代风险并加速产品上市。

半导体芯片行业封装测试环节的挑战

芯片封装测试不仅要实现芯片内部电路与外部引脚的精准电气连接,还需满足小型化、高性能、高可靠性的要求。例如,在先进封装技术如 BGA(球栅阵列封装)、QFN(四方扁平无引脚封装)等类型中,内部电路布局和引线键合的设计需要兼顾信号完整性、散热性能、高可焊性以及机械稳定性。

芯片研发制造过程中,涉及多个版本的迭代优化。封装测试设计需要与芯片设计紧密配合,确保不同版本的封装设计与芯片的电气特性和工艺要求相匹配。同时,封装测试团队内部以及与芯片设计团队之间需要高效的协同设计机制,以避免因信息不对称导致的实际错误和返工。

芯片封装测试中的封测工艺极为复杂且精度要求高。不同的封装形式需要精确设置封测参数,如键合线的长度、弧高、拉力等。在 Wire Bonding 环节,微小的参数偏差可能导致短路、断路或接触不良等质量问题,影响芯片封装的可靠性和性能,从而影响到整个芯片量产的上市周期。

在 3D IC 中,多个半导体芯片垂直堆叠,引线键合对于连接这些层至关重要。随着设备变得越来越紧凑,对高密度处理能力的需求也日益增长,使得引线键合在管理细间距和高引脚数方面不可或缺。这项技术对于高性能计算、先进的移动设备和高密度数字电子产品至关重要。如下图为 X-Ray 拍出来的图像:采用引线键合的 3D 堆叠芯片。

Altium Designer 的关键功能

及其在芯片封装测试中的应用

Altium Designer的版本控制功能为芯片封装测试环节提供了强大的管理工具。在芯片后期的板级测试过程中,以及芯片量产出品后的相关参考设计板的提供阶段,每一次的修改都会被详细记录。包括修改时间、人员及具体内容。例如,某芯片封装测试项目在迭代优化过程中,工程师通过版本控制功能,可以清晰追溯不同版本的封装相对应的设计文件,快速定位到特定版本进行测试验证。当发现新的封装及设计文件存在问题时,能够方便地回溯到上一稳定版本,分析问题根源并进行针对性优化。这不仅确保了设计文件的可追溯性和一致性,还极大地提高了多版本管理的效率,避免了因版本混乱导致的项目延误。

在芯片封装测试中,装配变量功能发挥着至关重要的作用。它可以定义多种装配方案和参数设置,以适应不同封装形式和测试要求。例如,在进行不同尺寸的芯片封装时,通过设置装配变量,可以快速调整键合线的材质、直径、弧高等参数。在实际测试中,工程师可以根据测试需求快速切换装配变量,模拟不同的装配场景,从而提前发现潜在的装配问题。例如,某封装测试企业在对一款新型芯片进行 Wire Bonding 测试时,利用装配变量功能,快速调整键合线的拉力和弧高参数,成功解决了键合不良的问题,提高了封装测试的一次合格率。

极坐标应用在芯片测试环节具有独特的优势。有些芯片测试板需要采用圆板布局布线,其电路布局和引线连接往往呈现出一定的对称性和规律性。通过极坐标系,可以更加直观地进行测试板的布局和布线设计。在圆板的布局布线过程中,利用极坐标可以更精准地定位元器件的相应位置,确保布线的连接精度。例如,在设计一款圆形芯片测试板的方案时,工程师可以使用极坐标系,将待测芯片按照角度和半径进行整列式分布,从而实现高效、精准的芯片后端测试工艺,并适当配置相应的参数。这不仅提高了半导体芯片的测试效率,还降低了因测试板中待测芯片定位不准确导致的良率影响。

Altium Designer 对 Wire Bonding 工艺提供了全面的支持,是芯片封装测试中不可或缺的工具。它可以帮助工程师进行键合线的路径规划、长度优化以及应力分析等。通过精确的模拟和计算,确保键合线在芯片封装过程中不会出现短路、断路或接触不良等问题。例如,某半导体企业使用 Altium Designer 进行 Wire Bonding 设计时,通过软件的优化算法,成功设计出键合线的适当长度,线间间距,和绑线方式,提升了芯片的封装工艺和封装良率。在实际封装测试中,工程师可以根据软件的分析结果,调整键合工艺参数,如键合头的压强、键合时间等,进一步提高键合质量。这不仅提升了芯片封装的可靠性,还降低了生产成本。

此外,在半导体芯片封装领域,裸片COB(Chip on Board)封装凭借其成本低、散热好等优势,也被众多中小企业广泛应用。Altium Designer 的 Wire Bonding 功能在裸片 COB 封装中,更是发挥了重要作用。在裸片COB封装中,工程师可以利用该功能根据裸片的尺寸、引脚间距以及基板的布局,优化键合线的路径和形状,确保键合线的连接既稳定又可靠,避免因键合线过长或过短导致的信号传输延迟或接触不良等问题。它能帮助工程师自动识别和避开潜在的键合区域障碍物,可以灵活配置,在半导体芯片与其封装之间,或多芯片模块内的不同芯片之间建立安全、低电阻的电连接。防止引线之间的短路或接触不良,从而提高键合工艺的良品率。如下图为 Altium Designer 的 Wire Bonding 功能在板上芯片 (COB) 技术的应用。

应用案例

一家知名半导体芯片封装测试企业承接了一款高性能芯片的封装项目。该芯片采用先进的 BGA 封装技术,内部电路复杂,封装密度高。在项目初期,封装测试团队面临诸多设计难题,如键合线布局不合理导致信号干扰严重,封装散热性能不佳等。通过引入 Altium Designer 的版本控制、装配变量、极坐标应用和 Wire Bonding 功能,工程师们对不同版本的封装设计进行了深入分析和比对。快速调整键合线的材质、弧高等参数,优化键合线布局;结合极坐标应用,精准定位键合点位置,提高键合效率和精度。最终,成功解决了信号干扰和散热问题,芯片封装测试合格率大幅提高,产品性能显著提升,提前完成了项目交付。

在一款芯片的迭代研发过程中,芯片设计团队和封装测试团队紧密合作。芯片设计团队频繁对芯片内部电路进行优化调整,导致封装测试设计需要不断适应新的电气特性和引脚布局。通过 Altium Designer 的版本控制功能,封装测试团队能够及时追溯以往的版本并及时更新,确保封装测试设计与芯片设计的一致性。在 Wire Bonding 环节,依靠软件分析,快速调整装配参数,适应芯片引脚的变化。同时,通过极坐标应用进行键合点的重新定位和优化。最终,芯片的迭代研发周期缩短了 25%,封装测试的一次合格率提高了 30%,产品性能和可靠性得到了显著提升。

LED:COB 技术广泛应用于 LED 设计,可提供更高的流明密度和更佳的热管理。引线键合技术可实现紧凑的 LED 阵列,并具有高效的散热性能,从而为汽车、工业和消费电子应用提供更明亮、更持久的照明解决方案。如下图所示为 COB LED 阵列。

光电子器件和图像传感器:随着图像传感器分辨率的提高,所需的连接数量也急剧增加,细线键合技术变得至关重要。这些高性能、高密度的设计对于先进的消费电子产品、医疗诊断和安全系统大有裨益。如下图所示为采用引线键合的 CMOS 图像传感器 COB。

Altium Designer 助力半导体

芯片封装测试行业创新发展

Altium Designer 的高效设计工具能够显著缩短半导体芯片封装测试的研发周期。其版本控制功能方便团队成员快速定位所需版本,装配变量功能可以快速调整芯片测试装配方案,极坐标应用和 Wire Bonding 功能则为封装和测试提供了精准的解决方案。这些功能的有机结合,使得芯片封装测试设计和工艺优化过程更加高效、流畅,大大缩短了芯片上市周期。

随着半导体芯片行业向更高性能、更小尺寸、更低功耗方向发展,Altium Designer 也在不断更新和优化其功能。例如,支持更复杂的芯片封装的相关设计、更精细的为半导体芯片应用提供相应的高速高密度布局布线、以及更高效的进行板级信号完整性分析等。它能够很好地适应行业的发展趋势,为芯片封装测试以及各芯片类型的实际应用提供持续的技术支持和创新动力。

Altium Designer凭借其强大的版本控制、装配变量、极坐标应用和 Wire Bonding 等功能,在半导体芯片封装测试行业展现出了巨大的应用价值。它不仅能够应对当前芯片封装测试的复杂性挑战,还能助力工程师们进行创新设计,推动半导体芯片封装测试技术以及芯片实际应用的发展。为我国半导体芯片产业的自主可控和创新发展提供了强力支持。

通格创智是达索SOLIDWORKS大中华区核心经销商和增值服务商,同时也是电子设计自动化(EDA)软件Altium、ARM在中国的核心合作伙伴。如有采购Altium Designer软件,可来电联系我们:400-112-8028

行业新闻

行业新闻

客户案例

技术文章

行业新闻

技术文章

行业新闻

行业新闻

行业新闻